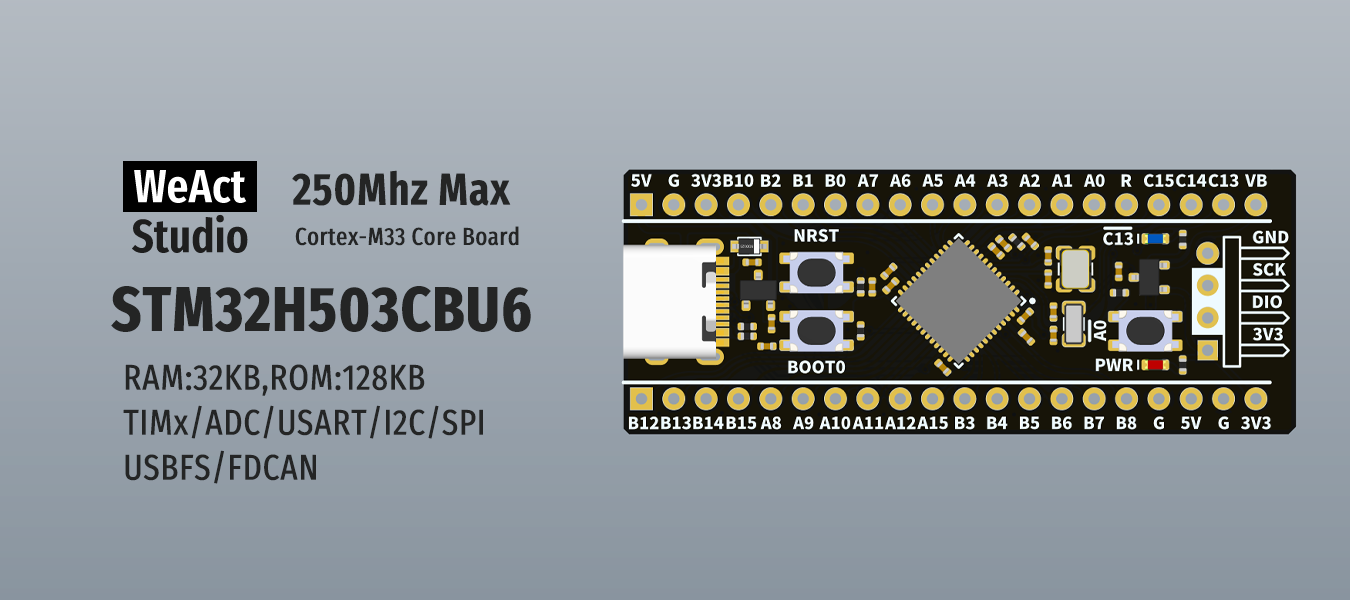

stm32h5 seemed to be a fairly new product line too

https://www.st.com/resource/en/datashee ... h503eb.pdf

cortex M33

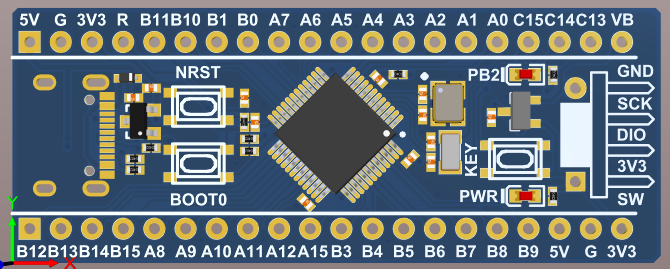

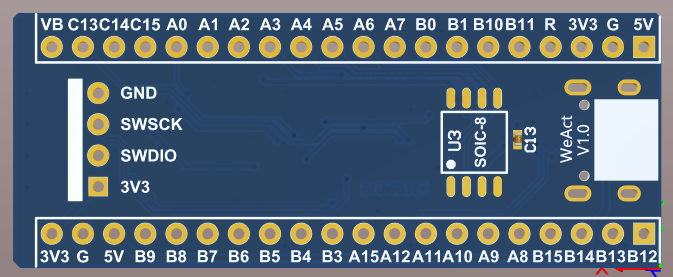

quite similar to this I'd guess

viewtopic.php?t=2477

it is more like the F4 / G4 series with ART accelerator and all

I've got a H7 board

https://github.com/WeActStudio/WeActStu ... iSTM32H723

H7xx is apparently quite a different thing

https://www.st.com/resource/en/datashee ... h723zg.pdf

Cortex M7 with its own caches lines etc, the clock setup is also quite different from e.g. the F4xx, Cortex M4 series

H7 has system clocks that can literally be 'untangled' from the peripherals clocks

I'd guess the purpose is so that the cpu clocks can be changed on the fly without affecting IO which may require a fixed and/or lower clock speeds.

but that that setup is more 'complicated' vs F4 etc

for Cortex M33 accordingly it has an FPU

but that apparently it is same as F4

https://community.arm.com/support-forum ... -cortex-m4

while the simplified view of the FPU registers is like such

https://developer.arm.com/documentation ... -registers

what is often less mentioned are that the floating point registers are also mapped as vector registors

https://developer.arm.com/documentation/ddi0553/latest/

^ it is 'briefly' covered in chapter B5 of the Arm-v8M manual

those probably account for the Vxxx instructions covered in pm0264-stm32-cortexm33-mcus-programming-manual

3.10 Floating-point instructions

https://www.st.com/resource/en/programm ... ronics.pdf

that probably accounts for the "surprisingly fast" whetstone benchmarks seen in the F4 family

viewtopic.php?t=27

that makes it likely that those 'Mflops' are likely not bluff

viewtopic.php?p=939#p939

those could very well be deemed the 'DSP' instructions

those numbers rival 'old Intel Pentium 4' like 200 MFlops

http://www.roylongbottom.org.uk/whetstone%20results.htm

just that on Intel P4 that is double precision, so that is still a lot of difference

in hardware at least

but the single precision FPU speeds makes it possible to do various DSP tasks in real time that would likely otherwise be not feasible.